基本信息:

- 专利标题: LOW POWER ADC FOR HIGH DYNAMIC RANGE INTEGRATING PIXEL ARRAYS

- 专利标题(中):低功率ADC用于高动态范围集成像素阵列

- 申请号:US14492310 申请日:2014-09-22

- 公开(公告)号:US20150288376A1 公开(公告)日:2015-10-08

- 发明人: Stephen Gaalema , William Bahn , David Dobyns , Tue Tran

- 申请人: Stephen Gaalema , William Bahn , David Dobyns , Tue Tran

- 申请人地址: US CO Colorado Springs

- 专利权人: BLACK FOREST ENGINEERING LLC

- 当前专利权人: BLACK FOREST ENGINEERING LLC

- 当前专利权人地址: US CO Colorado Springs

- 主分类号: H03M1/12

- IPC分类号: H03M1/12

摘要:

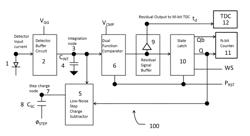

In one or more embodiments, an apparatus and method for processing an analog signal into a digital signal includes an input current buffer circuit, a signal charge integration node, a dual function comparator, a step charge subtractor, a state latch, a coarse N-bit counter, an optional residue signal buffer and a residue signal M-bit time-to-digital (TDC) converter. The circuitry is free running, meaning that it is never reset. Instead, what is tracked for each frame is how much additional charge has been accumulated since the end of the previous integration period. Between each frame, the state of the counter and the amount of charge residing in the integration node are recorded. This information from the beginning and end of a given frame is differenced and to this is added the amount of charge indicated by the number of times the counter overflowed during the integration period.

摘要(中):

在一个或多个实施例中,用于将模拟信号处理成数字信号的装置和方法包括输入电流缓冲电路,信号电荷积分节点,双功能比较器,步进电荷减法器,状态锁存器,粗略N- 位计数器,可选的残留信号缓冲器和残留信号M位时间数字(TDC)转换器。 电路是自由运行的,这意味着它永远不会重置。 相反,每个帧跟踪的是从上一个积分期结束以来累积了多少额外费用。 在每个帧之间,记录计数器的状态和驻留在积分节点中的电荷量。 来自给定帧的开始和结束的信息是不同的,并且由此增加由计数器在积分期间溢出的次数所指示的费用量。

公开/授权文献:

IPC结构图谱:

| H | 电学 |

| --H03 | 基本电子电路 |

| ----H03M | 一般编码、译码或代码转换 |

| ------H03M1/00 | 模/数转换;数/模转换 |

| --------H03M1/12 | .模/数转换器 |